Innovation is the key to the future, but R&D is the key to the future innovation

Think Silicon’s R&D team addresses today the challenges that shape the technology of the future!

OUR APPROACH

At Think Silicon, our mission is to create leading technology for the global market shaping the products of the future. We always strive to expand the limits of technological possibilities, to engage people in technology, and to create a more sustainable world.

Think Silicon® is a research-bound company. Looking for answers is a fundamentally important part of what we do and it has formed Think Silicon’s identity. Our strong belief is that research is not an end in itself neither a constant race to develop new technologies, but it is rather something that makes a tangible contribution to improving the quality of people’s lives. Without research, there can be no progress. And without progress, we cannot improve the quality of people’s lives.

The majority of our IP and products have their routes back to the excellent Research and Development division of the company along with the strong academic background of our engineers. Our R&D team aims at making discoveries that impacts everyone’s life, and core to our approach is sharing our research and tools to fuel progress in the field. Our researchers publish regularly in academic journals and incorporate research to our products.

Think Silicon® is currently active in several European and Greek Research funded Programs, constantly developing and evaluating solutions that will result to cutting-edge products.

RESEARCH AREAS

Ultra-Low Power Graphics Processing

GPU-WEAR

GPU-WEAR is an Horizon 2020 EU-funded project into low-power graphics devices under the topic SME Instrument Phase II. The project has started on June 1, 2016 with a grant of € 1.34 M ($1.56) targeting to advance the technology readiness level and commercialization of the NEMA® ultra-low power graphics platform.

NEMA® GPU-WEAR is a novel platform to develop and implement ultra-low power, heterogeneous, multicore Graphics Processing Unit (GPU) technology, for SoCs (System on the Chip). The aim is to extend the battery life by decreasing the power-consumption by an order of magnitude for the next generation of mobile, wearable and embedded devices while running fast, graphically rich display and 4K video applications.

Information & Specifications

Dealing with the levels of power consumption required by wearables and Internet of Things (IoT) devices represents a major technological challenge that demands novel multi-disciplinary approaches spanning circuit, architecture, compiler, and API level optimization techniques. The main challenge in these new devices is the battery life and how to extend it to more than one day without having to search for wall plugs and charging stations. Thus, ultra‐low power devices performing energy‐conscious graphics calculations are urgently needed in the market. GPU‐WEAR is designed to further refine and validate the first heterogeneous multicore embedded graphics processing unit (GPU), the associated low‐power software library, and the run‐time system explicitly optimized for the ultra‐low power requirements posed by the wearables/IoT market.

The envisaged heterogeneous GPU includes two different types of general purpose (GP)‐GPU cores with different microarchitectures. The unique selling point of the project’s output is that both core types are enabled by a single and disruptive low‐power Instruction Set Architecture (ISA), thus relying on a single executable and software/compiler toolchain. In addition, GPU‐WEAR will release an integrated software environment, in the form of a Software Development Kit (SDK), referred to as GPU‐WEAR‐SDK, to streamline the development process of graphics and non-graphics applications.

NEMA Graphic Engines

Think Silicon's GPUs NEMA® | t (NEMA® tiny) and NEMA® | S (NEMA® SMALL) are based on a disruptive Very Long Instruction Word (VLIW), highly multithreaded microarchitecture powered by compamy’s proprietary vectorized, Single Instruction Multiple Data (SIMD) and low-power ISA. Think Silicon® ISA encapsulates three types of parallelism (VLIW, SIMD, & Vector processing) – the key enabler for full hardware utilization, thus ultra-low power consumption. These GPUs can exploit the imbalance in graphics workloads by building a heterogeneous multicore GPU that can reduce power consumnema_logoption by more than an order of magnitude.

To this end, as part of the project, the company integrated the SMALL.GPU (based on NEMA® | S) with the tiny.GPU (based on NEMA® | t). This will create the first heterogeneous, multicore GPU in the market of wearable devices. While, NEMA® | t and NEMA® | S represent today the most competitive solutions in the field of tiny and SMALL GPUs respectively, their combination will inherit the well-known benefits of heterogeneous computing. As part of the project, Think Silicon is currently developing novel policies to best-balance graphics workloads between NEMA® | S and NEMA® | t in the most energy-efficient manner and novel compression techniques in all GPU levels (geometry, pixel, framebuffer, and texture compression) to minimize memory requirements and bandwidth.

GPU-WEAR Objectives

GPU-WEAR formulates a holistic approach (at the hardware, software and API level) in reducing the power consumption of embedded/mobile GPUs. The project has the following technical objectives:

Realize a family of novel heterogeneous embedded GPUs referred to as NEMA® | tS

Investigate and establish effectiveness of power reduction techniques in a holistic way

Develop a transparent to the programmer, display-aware, QoS-aware graphics library referred to as GPU-WEAR-LIBy

Optimize NEMA® | tS GPU for GPGPU soft real-time applications

Release GPU-WEAR-SDK to the Open Community and support its adoption

Set foundations for commercial exploitation

LPGPU2

Low-power GPUs have become ubiquitous. They can be found in domains ranging from wearable and mobile computing, to automotive systems. This places an ever increasing demand on the expected performance and power efficiency of the devices.

Future low-power system-on-chips will have to provide higher performance and be able to support more complex applications, without using additional power.

These demands cannot be met through hardware improvements alone, but the software must fully exploit the available resources. Unfortunately, application developers are seriously hindered when creating low-power GPU software by the limited quality of current performance analysis tools. In low-power GPU contexts there is only a minimal amount of performance information, and essentially no power information, available to the programmer. As software becomes more complex it becomes increasingly unmanageable for programmers to optimise the software for low-power devices.

This project proposes to aid the application developer in creating software for low-power GPUs by building on the results of the first LPGPU project by providing a complete performance and power analysis process for the programmer. This project will address all aspects of performance analysis, from hardware power and performance counters, to a framework that processes and visualises information from these counters, to applications that will be used as use-cases to drive the entire design. To access the new hardware performance counters a standardisable API will be produced to interface to a prototype hardware implementation. This will let the analysis and visualisation framework connect to any GPU driver that implements the API. The consortium’s expertise will be used to drive the initial design of the API and analyses, but multiple application use-cases will also be used to inform further iterations. This use-case driven approach will result in a performance and power optimisation framework that allows programmers to optimise applications in domains where there is a genuine need.

CONSORTIUM

TETRAMAX

Think Silicon participates in the ambitious tetramax (Technology Transfer via Multinational Application Experiments) project which is a Horizon 2020 innovation action aiming to provide an implementation of the European Smart Anything Everywhere (SAE) initiative in the domain of customized and low-energy computing for cyber-physical systems and the Internet of Things (IoT).

It is built up from a consortium of leading-edge European academic institutions, European SMEs, start-ups, mid-caps, and major electronics corporations and OEMs. This setup facilitates especially the migration or adaptation of key customized low energy computing (CLEC) technologies from one industrial application domain to another. The composition of the project consortium will enable efficient multidisciplinary cooperation to help solving some of the most complex future industrial challenges, e.g. related to the industrial internet or autonomous driving. The total budget of the tetramax project is 7M€ and is coordinated by RWTH Aachen University, with 22 partners, covering almost all EU countries and will run for four years.

On September 19th, 2017 tetramax was officially launched! 22 partners from all over Europe gathered in Aachen and joined forces to become the leading competence center network for customized and low-energy computing. RWTH Aachen University hosted a one-day event during which the official launch of the tetramax project took place. Besides the formal project kick off, the meeting provided an opportunity for all partners to meet, obtain an overview of the entire project and initiate the first interactions.

For more information please visit the project’s public website from here.

CONSORTIUM

Compiler and Code Transformations

VIPGPU

The VipGPU project aims at developing new hardware and software technology to efficiently support cutting edge application scenarios, which have the potential of significant research, business, and financial gains:

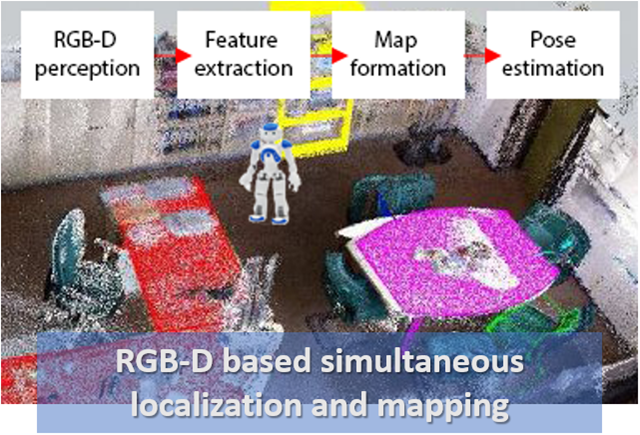

a. A computer vision application for mobile robotics, and

b. a virtual reality application for medical training for surgical procedures. The project will deliver a FPGA prototype based on the multicore, heterogeneous GPUs of Think Silicon that will be optimized for the two use-cases.

More specifically, we have the following goals:

- Enhanced Low Power GPUs and Hardware Accelerators. The first objective of the project is to develop the FPGA prototype consisting of very low power multiple GPUs and supporting the OpenCL 2.0 and Vulkan programming models. Also, customized low-level libraries will be created that will run on the GPU of Think Silicon and will be optimized based on its architecture. The FPGA prototype will include hardware accelerators for the most performance-critical functions of these two applications. Specialized accelerators can offer the greatest possible performance, since they are precisely tailored to the algorithm requirements. These accelerators will be integrated in Think Silicon’s GPUs.

- Machine Vision in Mobile Robotic Systems. Mobile robotic systems are used, inter alia, for educational purposes or for supporting older people. The first application of the project will accurately determine the position of a robot and at the same time map its surroundings through visual processing. The computation of this information is a very important process of an autonomous robotic system, as it updates a series of other processes, such as gait design, perception and understanding of the surroundings, routing, etc. Highly accurate algorithms are based on computationally intensive processes, which prevent them from being applied to portable devices and small / medium-size robotic systems. In order to limit these power and computational dependencies, researchers very often resort to several compromises, which result in efficiency and robustness reductions of the proposed algorithms. In this project, we aim to develop a positioning system for embedded systems so as:

a. to determine the exact position of a robot in real time conditions,

b. to enable dynamic image processing, in poor lighting conditions and changing scenes,

c. to create a low-power processing subsystem that will not use the processing power of the robot.

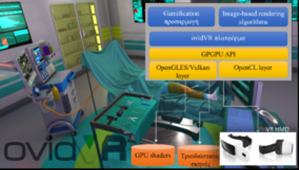

- Virtual reality. The second application is to create an innovative environment for creating new generation training games that will take full advantage of new real-time virtual reality and motion detection technologies. Recognizing the current state of technology and market needs, the partners will expand their existing technology and know-how with new algorithms that will allow:

a. Simulation in a virtual reality environment of an application for orthopedic surgeon training.

b. The stereoscopic display in a new portable personal projection system based on the new very low-power GPUs that will not be connected to a personal computer, and

c. The creation of educational games for medical surgeon training in a simplified way.

The expected results will lead to the creation of an ideal system for the visualization of medical simulation and experiential education in processes and events.

CONSORTIUM

CNN/DNN accelerators

DEEP- EVIoT: Deep embedded vision using sparse convolutional neural networks

In recent years, there has been a large and ever increasing growth interest in computer vision applications for embedded portable IoT devices, while at the same time satisfying high performance, low computing cost and small storage requirements. The use of deep learning approaches increases the performance of such systems at very high levels having also demanding memory and power requirements.

The main purpose of the project is to design and implement an heterogeneous platform consisting of multiple Low Power Graphic processors with deep learning algorithms acceleration capabilities. A software SDK for vision problems using optimized deep sparse coding techniques especially designed for the aforementioned platform will be provided. The significant benefits of the proposed deep eviot system extends to a very wide range of applications from industrial and surgical robotics to autonomous vehicles, smart security cameras and military applications.

CONSORTIUM

Implemented within the framework of the action titled “SMEs support for research projects” and was co-financed by the European Union and National funds through the O.P. Western Greece 2014-2020 (project code: ΔΕΡ5-0018566)

HIGH-TECH AND AFFORDABLE 5G NETWORK ROLL-OUT TO EVERY CORNER

Affordable5G aims at creating a 5G network that will deliver a complete and affordable solution covering the needs of private and enterprise networks through technical innovation that span across all parts of 5G network, leveraging cell densification, RU/DU/CU split, hardware acceleration, edge computing and core network virtualization, seamlessly combined with the adoption of open source RAN, MEC and MANO solutions, for cloud-native, micro-service based deployments. To achieve its innovative and ambitious goal, the consortium brings together ten European SMEs, supported by MVNOs, system integrators and research institutes, grasping the opportunity to enhance their products, according to each company’s roadmap, while fostering collaboration among them. Affordable5G will offer a first-class opportunity to European SMEs to become frontrunners in the global 5G competition, facilitating them in their commercialization paths.

Affordable5G objectives:

Optimise 5G Hardware Elements

5G Dimensioning for dense deployments

Address network sharing strategies as cost-savings

Consolidate the usage of open platforms

In-system global testing, validation and evaluation

Business sustainability and competitive advantage

For more information please visit the project’s public website from here.

CONSORTIUM

The Affordable5G partners were carefully selected to provide complementary skills and competencies, which cover all project objectives and activities, starting from the generation of ideas, to analysis of requirements, to specification and design, low cost implementation, system integration, up to demonstration, validation and beyond.